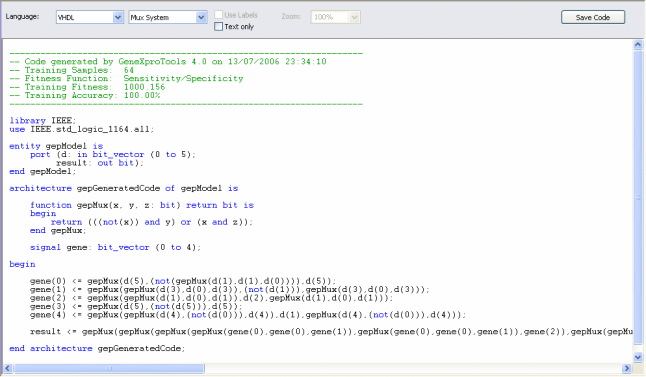

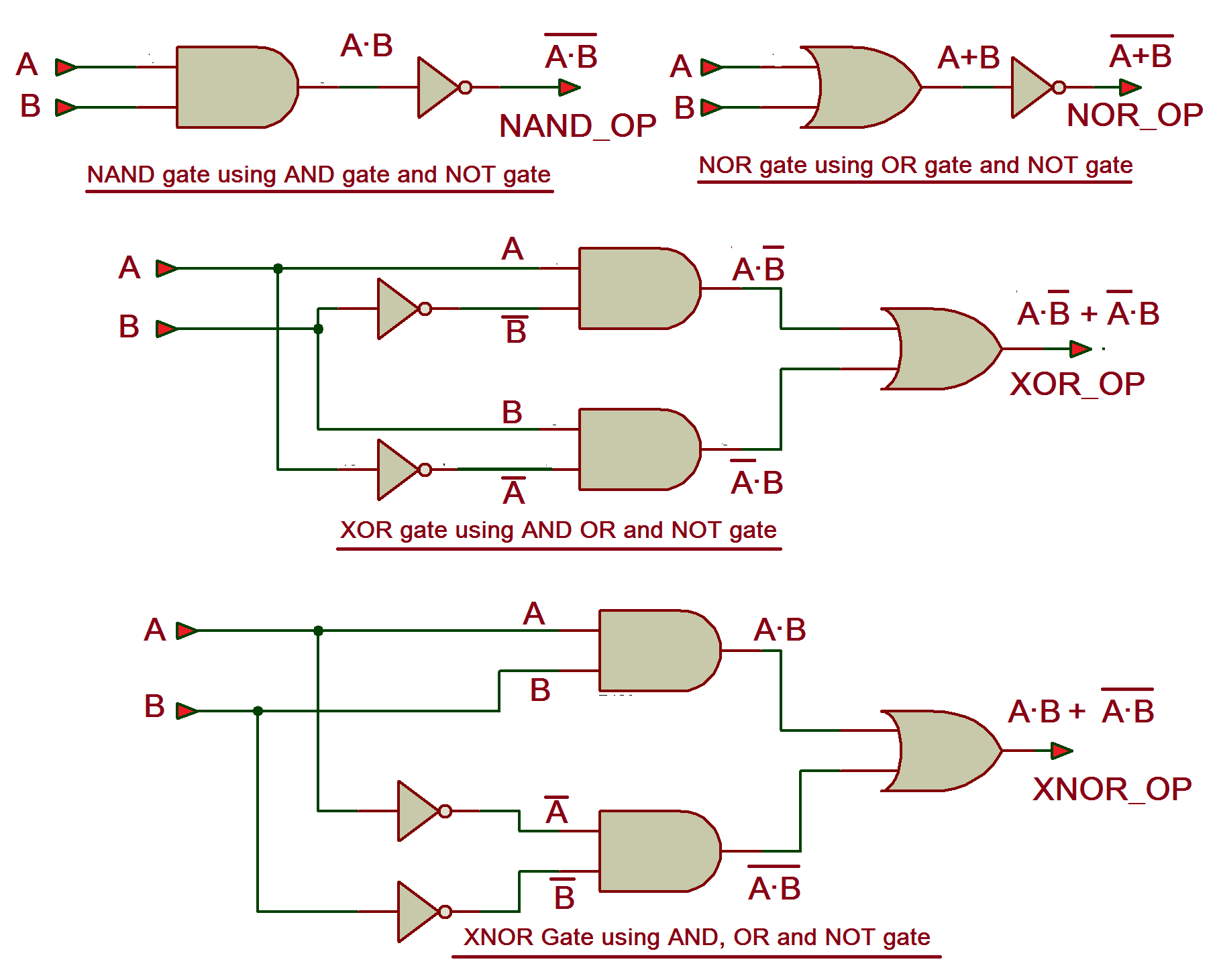

VHDL Tutorial – 5: Design, simulate and verify NAND, NOR, XOR and XNOR gates using AND-OR-NOT gates in VHDL

VHDL Tutorial – 5: Design, simulate and verify NAND, NOR, XOR and XNOR gates using AND-OR-NOT gates in VHDL

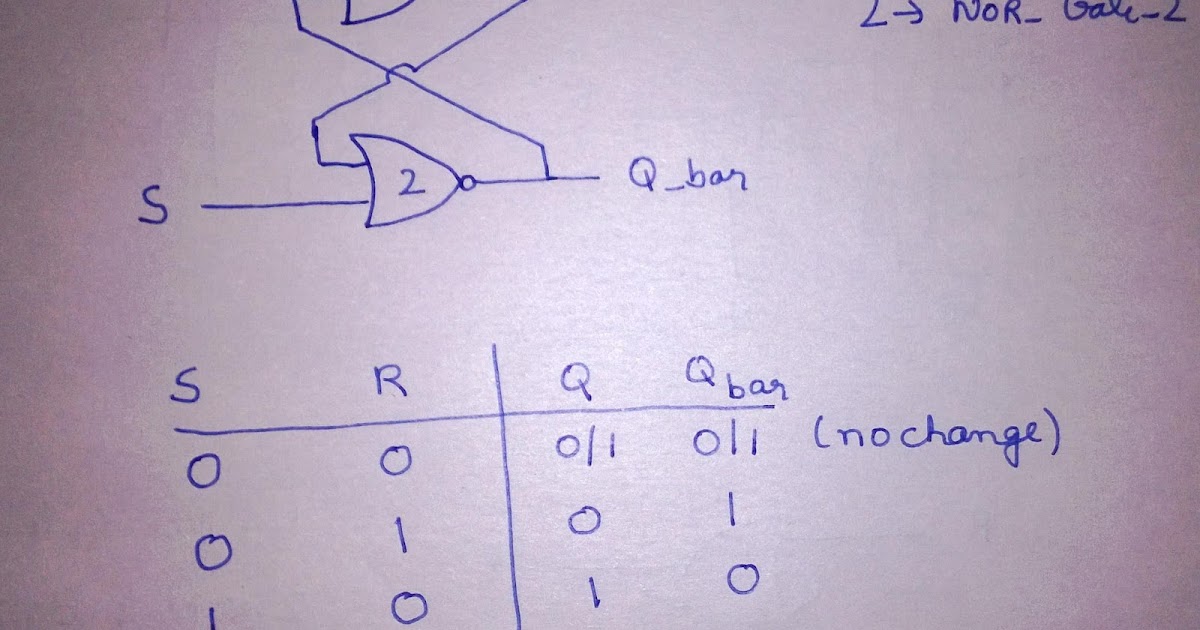

AND Gate: A Logic circuit whose output is logic '1' if and only if all of its inputs are logic '1'. - ppt download

![PDF] VHDL Implementation of nor Flash Controller | Semantic Scholar PDF] VHDL Implementation of nor Flash Controller | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/5453c05b0dd76ed01728c775565710acd256b46e/1-Figure1-1.png)